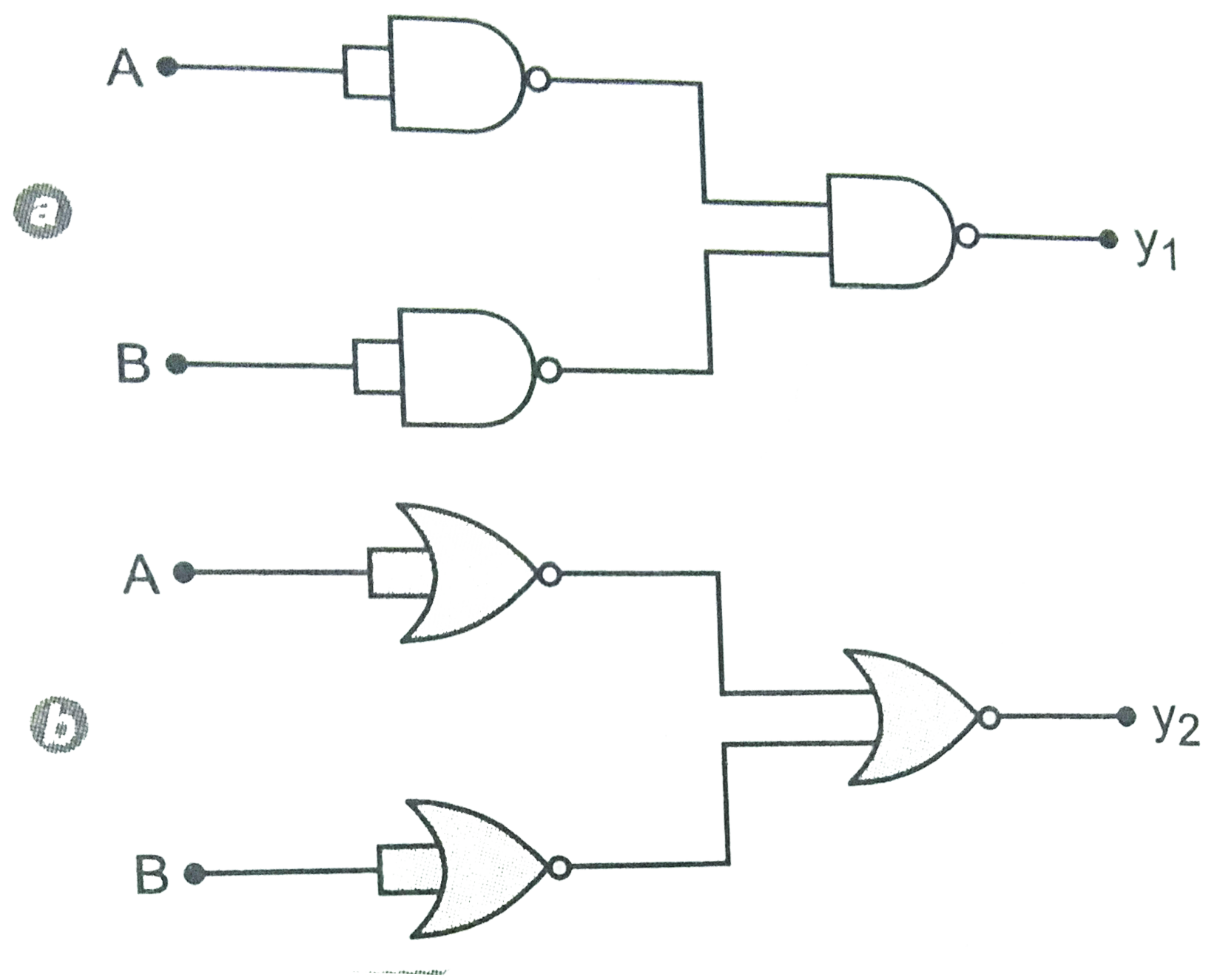

(i) For output `y_(1)`, we note that if either of A or B or both is 1, then output is 1. Hence this output `y_(1)` is of OR gate.

Three NAND gates connected as shown in Fig. give OR gate.

(ii) For output `y_(2)` , we note that if both A or B are 1, then only output `y_(2) =1`. Heance this output `y_(2)` is of AND gates. Three NOR gates connected as shown in Fig. gives AND gate.