Text Solution

Verified by Experts

Topper's Solved these Questions

Similar Questions

Explore conceptually related problems

NARAYNA-SEMICONDUCTOR ELECTRONICS-ADDITIONAL EXERCISE (ASSERTION AND REASON TYPE QUESTIONS :)

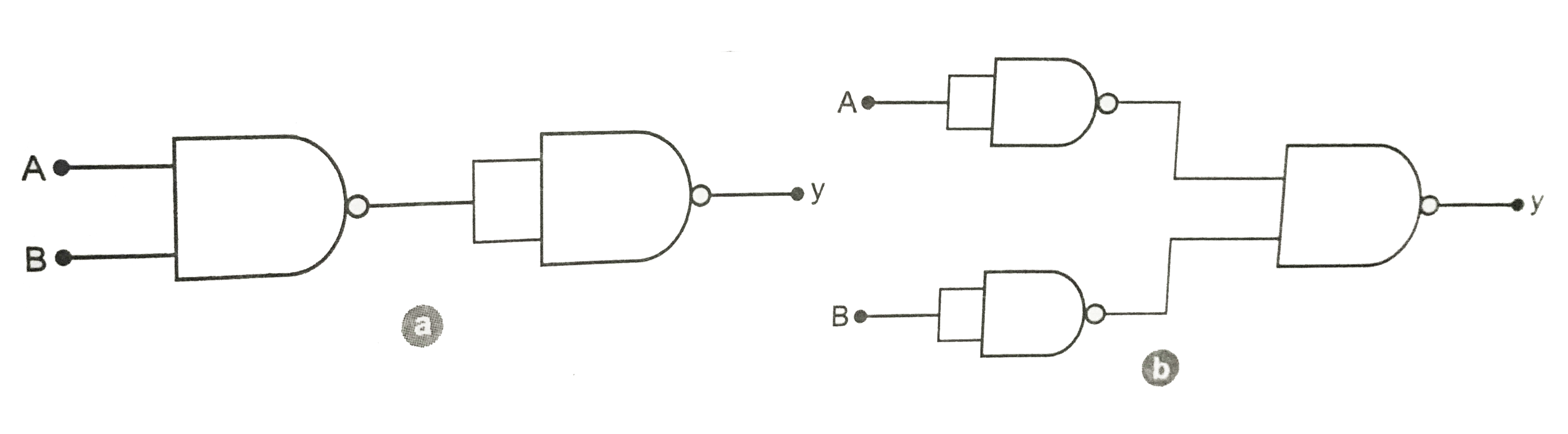

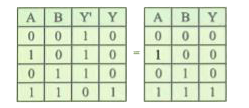

- You are given two circuit as shown in Fig.and . Which consists of NAND...

Text Solution

|

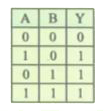

- Assertion : the following circuit represents 'OR' gate Reason : f...

Text Solution

|

- Assertion : In the following circuit the potential drop across the res...

Text Solution

|

- Assertion: NOT gate is also called inverter circuit. Reason: NOT gat...

Text Solution

|

- Assertion: The current gain in common base circuit is always less than...

Text Solution

|

- Assertion : The dominant mechanism for motion of charge carreis in for...

Text Solution

|

- Assertion : The value of current through p-n junction in the given fig...

Text Solution

|

- Statement-I : A p-n junction with reverse bias can be used as a photod...

Text Solution

|

- Assertion : In common base configuration, the current gain of the tran...

Text Solution

|

- Statement-I : Germanium is preferred over silicon for making semicondu...

Text Solution

|

- Assertion : The temparature coefficient of resistance is positive for ...

Text Solution

|

- Assertion : For a given applied voltage, conduction current in n-type ...

Text Solution

|

- Assertion : We cannot meausre that potential barrier of p-n junction b...

Text Solution

|

- Assertion : In Zener diode depletion layer is thin. Reason : In rev...

Text Solution

|

- Statement-I : A p-n junction with reverse bias can be used as a photod...

Text Solution

|

- Statement-I : When base region has larger width, the collector current...

Text Solution

|

- Statement-I : To be used as amplifier, the transistor in the common em...

Text Solution

|

- Assertion : A transistor amplifier operates in active region. Reason...

Text Solution

|

- Assertion: NAND or NOR gates are called digital building blocks. Rea...

Text Solution

|

- Assertion : In transistor, common emitter configuration is used to mak...

Text Solution

|